# **ARM VIDC20**

## **Data Sheet**

Document Number: ARM DDI 0030E Issued: Feb 1995

Copyright Advanced RISC Machines Ltd (ARM) 1995

All rights reserved

#### **Proprietary Notice**

ARM and the ARM Powered logo are trademarks of Advanced RISC Machines Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this datasheet may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this datasheet is subject to continuous developments and improvements. All particulars of the product and its use contained in this datasheet are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This datasheet is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this datasheet, or any error or omission in such information, or any incorrect use of the product.

#### **Change Log**

Issue Date By Change

E Feb 1995 BJH Updates to signal descriptions and pins.

#### **Preface**

The VIDC20 is a highly flexible video controller capable of meeting the needs of a wide range of video requirements. The device is highly programmable and can be used in many different system configurations. The device will directly drive colour monitors and also has a LCD driver for direct interfacing of LCD screens for portable computer products. Hi-resolution monochrome monitors may also be driven at pixel rates of up to 400 MHz with minimal external hardware.

The device also supports two stereo sound systems, one featuring up to eight channels each with its own stereo position, and the other, a serial sound port suitable for connection to an external CD DAC.

#### **Applications**

- Desktop computers

- Portable computers

- PC video cards

- Graphics engines

- Multimedia

- Portable consumer products

#### **Feature Summary**

- VGA, Super VGA, and XGA resolution

- 8 bits, giving 16M colours

- Direct driving of LCD and CRT screens

- 1, 2, 4, 8, 16, 32 bits per pixel

- 1.0 micron CMOS process

- Up to 100MHz pixel rate

- Low power onsumption

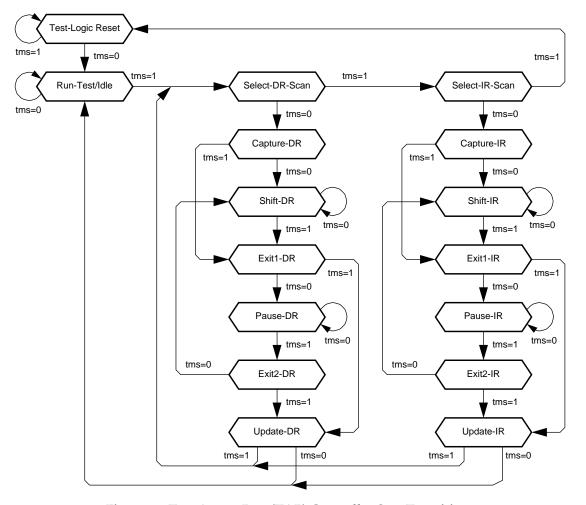

- IEEE 1149.1 boundary scan

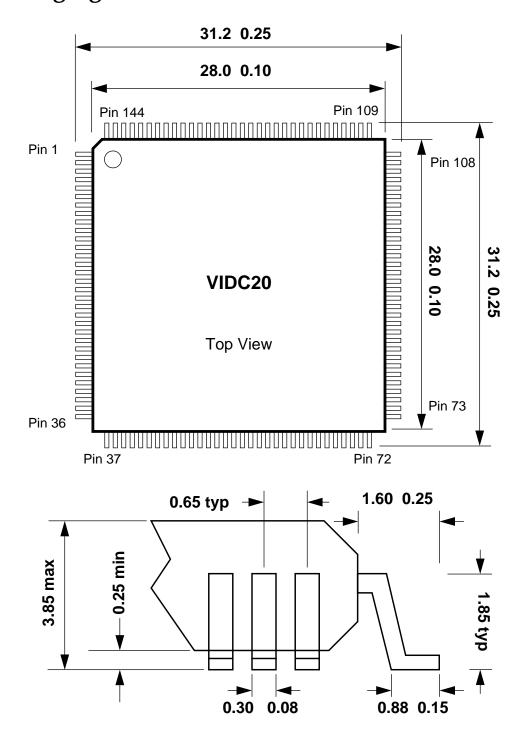

- 144 PQFP package

## **Table of Contents**

| 1.0  | Introduction                                                                               | 1            |

|------|--------------------------------------------------------------------------------------------|--------------|

|      | 1.1 Typical System Configurations                                                          | 1            |

|      | 1.2 Major Features                                                                         | 2            |

|      | 1.3 Block Diagram                                                                          | 4            |

| 2.0  | Signal Description                                                                         | 5            |

|      | 2.1 Key to Signal Types                                                                    | 8            |

| 3.0  | System Configurations                                                                      | 9            |

|      | 3.1 Asynchronous 32 bit mode                                                               | 9            |

|      | 3.2 Synchronous 32 bit mode                                                                | 10           |

|      | 3.3 64 bit mode                                                                            | 10           |

|      | <ul><li>3.4 Split Bank mode</li><li>3.5 Using VRAM with VIDC20</li></ul>                   | 11<br>11     |

|      | 3.6 Display Options                                                                        | 13           |

| 4.0  | Programming Model                                                                          | 15           |

| 1.0  | 4.1 VIDC20 Registers                                                                       | 15           |

| 5.0  | Pixel Clock                                                                                | 31           |

| 6.0  | Setting the FIFO preload value                                                             | 33           |

| 7.0  | The Palette                                                                                | 35           |

|      | 7.1 Palette Updating                                                                       | 35           |

| 8.0  | Cursor                                                                                     | 37           |

|      | 8.1 Cursor in HiRes Mode                                                                   | 37           |

|      | 8.2 Cursor in Interlace Mode                                                               | 37           |

|      | 8.3 Cursor in LCD mode                                                                     | 38           |

| 9.0  | Hi-Res Support                                                                             | 39           |

|      | 9.1 VIDC20 Support for Hi-Res Mode                                                         | 39           |

| 10.0 | Liquid Crystal Displays                                                                    | 41           |

|      | 10.1 LCD grey-scaling                                                                      | 41           |

|      | <ul><li>10.2 Dual Panel LCDs (Duplex Mode)</li><li>10.3 Single Panel Colour LCDs</li></ul> | 42<br>42     |

| 11 0 |                                                                                            |              |

| 11.0 | External Support 11.1 The External Port                                                    | <b>43</b> 43 |

|      | 11.2 Power Saving Considerations                                                           | 43           |

|      | 11.3 Vertical and Horizontal Synchronisation                                               | 44           |

|      | 11.4 Genlocking                                                                            | 44           |

| 12.0 | Analog Outputs                                                                             | 45           |

|      | 12.1 DAC Control                                                                           | 45           |

|      | 12.2 Video DAC Currents                                                                    | 45           |

|      | <ul><li>12.3 Monochrome Output</li><li>12.4 ESD protection</li></ul>                       | 45<br>45     |

|      | 12.1 Lob procedure                                                                         | 43           |

| 13.0 | Soui | nd                              | 47 |

|------|------|---------------------------------|----|

|      | 13.1 | The Sound Core                  | 47 |

|      | 13.2 | VIDC10 Sound                    | 47 |

|      | 13.3 | The Serial Sound Interface      | 49 |

|      | 13.4 | Sound Outputs                   | 50 |

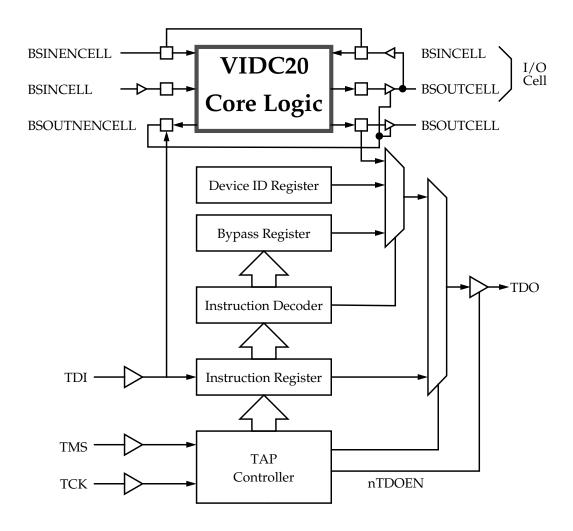

| 14.0 | Bou  | ndary Scan Test Interface       | 51 |

|      | 14.1 | Overview                        | 51 |

|      | 14.2 | Power -On Reset                 | 52 |

|      | 14.3 | Pullup Resistors                | 52 |

|      | 14.4 | Instruction Register            | 52 |

|      | 14.5 | Public Instructions             | 52 |

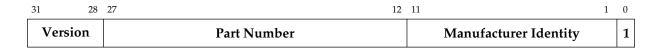

|      | 14.6 | Test Data Registers             | 56 |

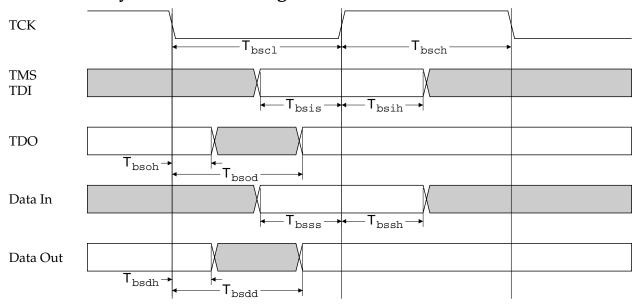

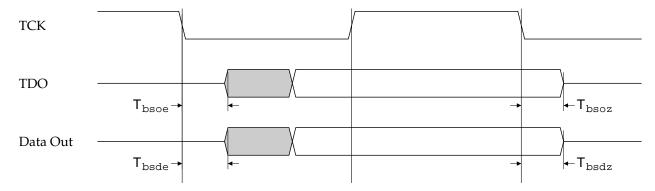

|      | 14.7 | Boundary Scan Interface Signals | 59 |

| 15.0 | Pack | kaging                          | 63 |

| 16.0 | Pino | out                             | 65 |

#### 1.0 Introduction

The VIDC20 offers the video system designer a flexible, high performance video controller for power and cost sensitive applications. The VIDC20 can be incorporated within a broad family of end products each with varying degrees of video requirements (e.g Portable LCD system through to higher performance Super VGA desktop products).

The VIDC20 flexible bus interface provides hardware support for interfacing to mixed memory systems (e.g. VRAM and DRAM) in conjunction with an external memory controller. The device also incorporates two stereo sound systems - an 8-bit (logarithmic) system, featuring up to eight channels each with its own stereo position, and an serial sound output port suitable for connection to an external CD DAC.

VIDC20 has a 64 bit data bus allowing a high data bandwidth (160 MByte/s) from an external memory system. VIDC20 takes data from these memory banks under DMA control. VIDC20 will however work with a 32 bit data bus, at a correspondingly lower bandwidth. Hence an entry level system is possible containing only one bank of DRAM. For higher resolution displays, VIDC20 can take its video data from VRAM, and on-chip hardware support is provided for this.

### 1.1 Typical System Configurations

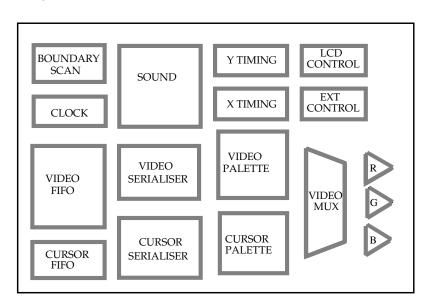

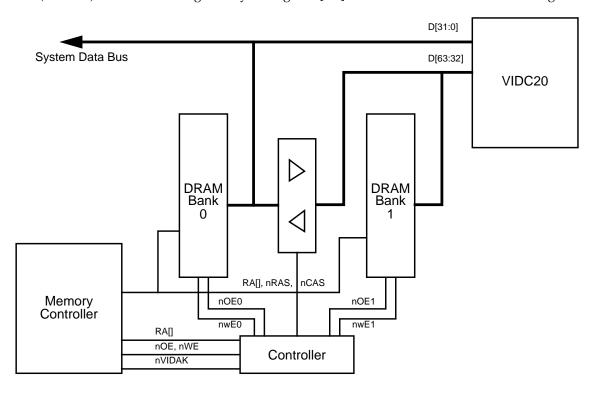

Figure 1: Typical Memory System Configurations

#### 1.2 Major Features

#### 1.2.1 Flexible Video System

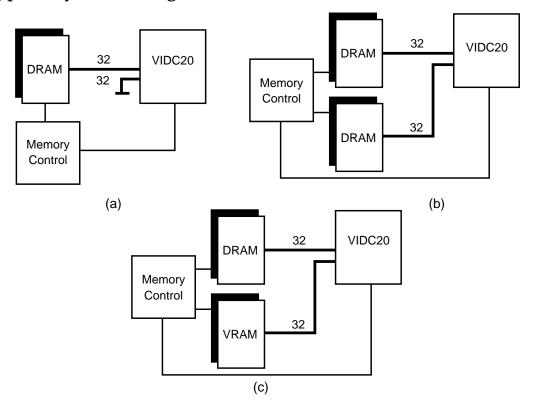

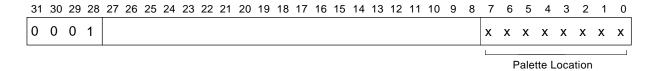

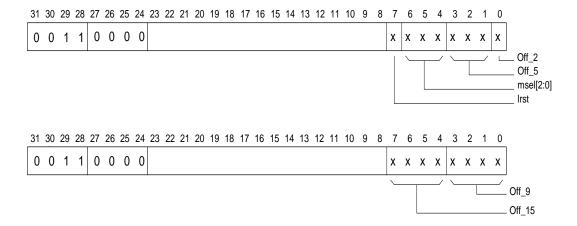

VIDC20 contains 296 write-only registers which offer a high degree of flexibility to the system programmer. 256 of these are used as the 28-bit video palette entries. These are programmed via an auto-incrementing address pointer. The remaining registers are specific control registers and allow the user to program the display parameters.

#### 1.2.2 Hardware Cursor

VIDC20 has a hardware cursor for all its display modes - HiRes, Interlace and LCD display modes. By offering cursor support on chip the designer benefits in terms of speed and lower software overhead, resulting in an improved *look and feel*. The cursor is 32 pixels wide and any number of pixels high and can be displayed in 4 colours including transparent from its own 28 bit wide palette. In this way a cursor of any shape and size can be defined within the 32 pixel wide limit.

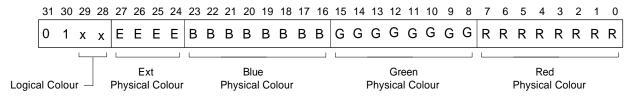

#### 1.2.3 Palette

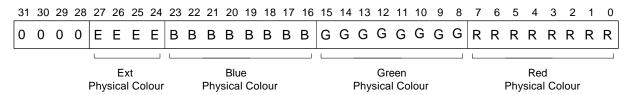

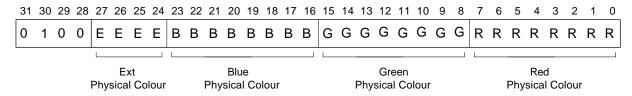

VIDC20 has a 28-bit wide 256-entry palette where each entry uses 8-bits for Red, 8 for Green and 8 for Blue, and 4 bits for external data. These external bits may be used outside the chip for a variety of purposes such as supremacy, fading, Hi-Res and LCD driving.

Look Up Tables (LUT) allow for logical to physical translation and gamma correction. The Red Green and Blue LUTs each drive their respective DACs, and the Ext LUT is normally configured to drive the 4 bit output port.

There are three 8-bit linear monotonic DACs (Red, Green and Blue) which give a total of 16 M possible colors. The DACs are designed to operate upto 100 MHz and drive doubly-terminated  $75\Omega$  lines directly.

#### 1.2.4 Pixel Clock

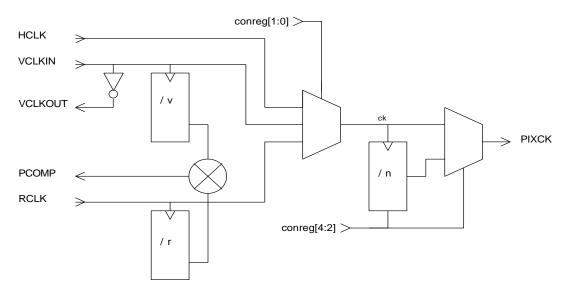

VIDC20 is capable of generating a display at any pixel rate up to 100MHz. The pixel clock may be selected from one of 3 sources, and then the selected frequency of this clock may be further divided down by a factor of between 1 and 8.

VIDC20 contains an on-chip phase comparator which, when used in conjunction with an external Voltage Controlled Oscillator (VCO), form a Phase Locked Loop. This configuration allows a single reference clock to generate all the required frequencies for any display mode thus obviating the need for multiple external crystals.

#### 1.2.5 Display Modes

Irrespective of the memory configuration used, VIDC20 is capable of many different display formats. In addition to the normal linear CRT display, VIDC20 can generate a true interlaced display, or can generate a display suitable for either very high resolution displays, single or dual-panel LCDs.

For CRT displays, VIDC20 is capable of operating in a variety of pixel modes - 1,2,4,8,16,32 bits/pixel. VIDC20 can also directly drive LCD displays in 1,2 or 4 bits per pixel via an internal 16-level grey scaler. The grey scaler algorithm adopted is patented.

#### 1.2.6 Power Management

The device is designed for power sensitive applications and incorporates design features to minimise power consumption. Typical power consumption for the device is 0.3 Watts. A *power down mode* allows power savings to be made when the device is not in use - e.g. in conjunction with a battery powered LCD system. Additional power sensitive features include the powering down of functions of the device currently not in use, such as the video DACs, sound DACs and the LCD grey scaler. In addition the palette design has been segmented such that only one eighth of the palette is enabled and clocked at any one time.

#### 1.2.7 On-Chip Sound System

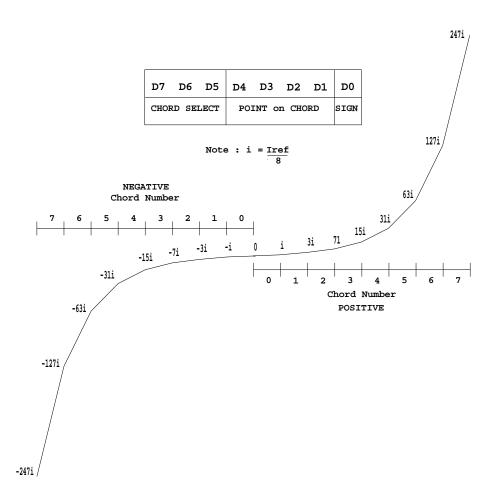

The VIDC20 supports two systems - an 8-bit (logarithmic) system using an internal dedicated DAC, featuring up to eight channels each with its own stereo position, and a 32-bit serial sound output suitable for driving external CD DACs.

In the 8-bit mode the device can work with 1,2,4 or 8 stereo channels, using time division multiplexing to synthesise left and right outputs. The sample rate is programmable through the Sound Frequency Register.

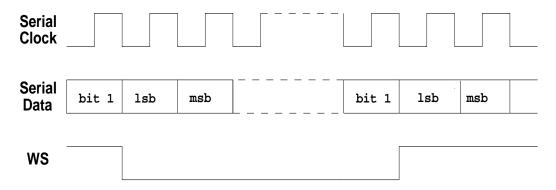

Enhanced 32-bit stereo sound is offered by the serial sound output which consists of a three pin serial interface. Each 32-bits sample consists of 16 bits for the left channel and 16 bits for the right channel.

### 1.3 Block Diagram

Figure 2: VIDC20 Block Diagram

## 2.0 Signal Description

| Name      | Pin                                                                                                   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-----------|-------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BOUT      | 39                                                                                                    | OA   | Blue Analog Output. The video signal analog outputs are designed to drive doubly-terminated 75 lines directly into a CRT.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| BUSCLK    | 123                                                                                                   | I    | Memory Bus Clock. When configured for a synchronous bus interface, this clock drives both VIDC20 and the memory system. It is used to latch data during sound and video DMAs. BUSCLK must be tied low in async mode.                                                                                                                                                                                                                                                                                                                      |  |

| DIN[63:0] | 121-117,<br>115-103,<br>101-100,<br>97-96,<br>94-88,<br>86-80,<br>76-67,<br>65-60,<br>58-53,<br>51-46 | I    | Data Bus In. All data to the chip is supplied on this bus. Data for register programming is always supplied on the lower half of the bus. When in async 32 bit mode, all data is supplied on the lower half of the bus, and the upper 32 bits should be tied low. When using VRAM, video data only is supplied on the upper half of the bus, and all other data on the lower half. When in split bank mode, interleaved DRAM provides 64 bit data during DMAs. See <i>Chapter 3.0 System Configurations</i> for details on architectures. |  |

| ECLK      | 22                                                                                                    | O16  | External Clock. When enabled, this clock validates the data on <b>ED[7:0</b> ]. In normal video mode, it runs at the pixel rate, but when LCD data is being produced, it runs at a quarter of the pixel rate.                                                                                                                                                                                                                                                                                                                             |  |

| ED[7:0]   | 12-14,<br>16-20                                                                                       | O8   | External Data. This is the digital output port of the chip. From this, the digital equivalent of the analog output may be produced in any colour, or data from the external palette may be produced. This may be used for a variety of purposes such as fading, supremacy, or serialisation for driving high resolution monitors. Also, data for driving LCD panels is output from this port. Data produced is validated by ECLK.                                                                                                         |  |

| EREG[1:0] | 5,6                                                                                                   | OS8  | External Register Data. The data from these pins is bits 1 and 0 of the external register. They may be used to control external devices.                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ESEL[1:0] | 7-9                                                                                                   | I    | External Data Select. These two bits determine the external port output. This may be either digital red, green or blue data, external data, or LCD data.                                                                                                                                                                                                                                                                                                                                                                                  |  |

| FLYBK     | 1                                                                                                     | OS8  | Fly Back. This gives information about the vertical display. It goes high at the start of the first raster not in display, and goes low again on the first raster in the active display. Frame buffer updates should be made during the fly back period for a flicker free display.                                                                                                                                                                                                                                                       |  |

| GOUT      | 40                                                                                                    | OA   | Green Analog Output. The video signal analog outputs are designed to drive doubly-terminated 75 lines directly into a CRT.                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| HCLK      | 125                                                                                                   | I    | High speed Clock.See Chapter 5.0 Pixel Clock for details of the clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

**Table 1: Signal Description**

| Name   | Pin | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

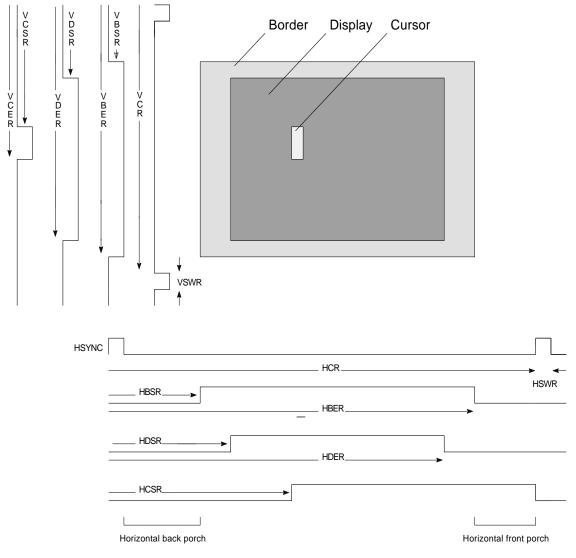

| HSYNC  | 31  | OS   | Horizontal Synchronisation. There are two synchronisation outputs on VIDC20, <b>HSYNC</b> and <b>VSYNC</b> . Dependant on the state of bits 17 and 16 in the external register, either horizontal or a composite (NOR) sync may be output on this pin, in either polarity. The width of the <b>HSYNC</b> pulse is definable in units of 2 pixels.                                                                                                                                                                                           |  |

| LS     | 27  | OA   | Left Analog Sound. Analog left hand stereo channel sound output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| nPROG  | 140 | I    | NOT Program. When this signal is low, data from <b>DIN[32:0]</b> is written to one of the registers. The register address is on the upper bits of the bus, and the data is on the lower bits of the bus.                                                                                                                                                                                                                                                                                                                                    |  |

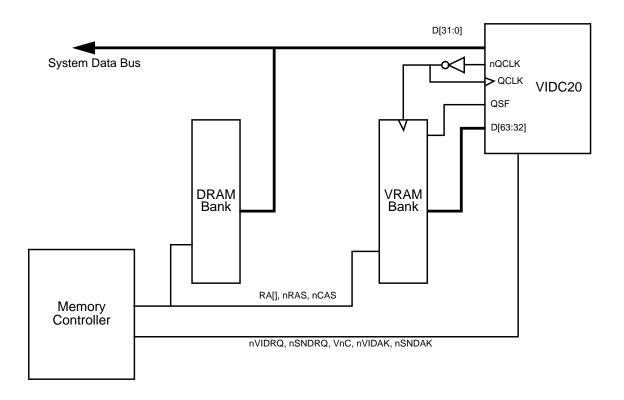

| nQCLK  | 132 | OS8  | NOT VRAM Clock. When in VRAM mode, this clock is output when data is required for the video FIFO. Externally, <b>nQCLK</b> must be inverted to make <b>QCLK</b> and fed back into VIDC20. It is the inverted version, <b>QCLK</b> that actually clocks the VRAM and thus validates the data. This scheme accounts for skew from clock loading.                                                                                                                                                                                              |  |

| nRESET | 143 | I    | NOT Reset. This is a level sensitive input signal which must be asserted during power up. The chip is forced into power down mode (bit 14 of the Control Register is set high), and thus a clock must be left running.                                                                                                                                                                                                                                                                                                                      |  |

| nSNDAK | 138 | I    | NOT Sound Acknowledge. This signal goes low to indicate that a sound DMA is taking place. Like its video counterpart, it has two timings dependant on the bus interface. Note that a sound DMA request is9 a request for 4 words of data.                                                                                                                                                                                                                                                                                                   |  |

| nSNDRQ | 135 | OS8  | NOT Sound Request. This signal goes low to initiate a sound DMA cycle. It is driven high again after <b>nSNDAK</b> falls.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| nVIDAK | 139 | I    | NOT Video Acknowledge. This signal goes low to indicate that video or cursor DMA is taking place. This signal has two timings, dependent on whether the bus interface is synchronous or asynchronous. In the synchronous case, <b>nVIDAK</b> is held low throughout the DMA, and data is clocked into the FIFO by <b>BUSCLK</b> . In the asynchronous case, data is strobed into the FIFO on the falling edge of <b>nVIDAK</b> . DMA is a request for 4 words of data so <b>nVIDAK</b> must be driven low 4 times in the asynchronous case. |  |

| nVIDRQ | 136 | OS8  | NOT Video Request. This signal goes low to initiate video DMA. If <b>VnC</b> is high, then the data transferred will be video data, otherwise it will be cursor. <b>nVIDRQ</b> is driven high again after <b>nVIDAK</b> falls.                                                                                                                                                                                                                                                                                                              |  |

| PCOMP  | 130 | O4   | Phase Comparator Output.See <i>Chapter 5.0 Pixel Clock</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| QCLK   | 133 | I    | VRAM Clock. See nQCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| QSF    | 142 | I    | Transfer Status Flag. This is an input from VRAM. When this signal changes state, it indicates that a VRAM transfer cycle can take place. This causes VIDC20 to start a video DMA which must be externally interpreted as a transfer cycle. See <i>Chapter 3.0 System Configurations</i> and <i>Applications Note 15</i> for details of connecting VRAM to VIDC20.                                                                                                                                                                          |  |

**Table 1: Signal Description**

## **Signal Description**

| NIDC20. This clock may also drive the sound system.  ROUT 41 OA Red Analog Output. The video signal analog outputs are designed to drive doubly-terminated 75 lines directly into a CRT.  RS 28 OA Right Analog Sound. Analog right hand stereo channel sound output.  SCLK 144 I Sound Clock. This signal can be used to clock the sound system, when a clock asynchronous to the video system is required. See Chapter 13.0 Sound.  SDCLK 3 OS8 Serial Data Clock. When the sound system is in serial sound mode, this clock output and validates serial data on its rising edge.  SDO/MUTE 4 OS8 Serial Data Out / Mute. This pin has two functions depending on whether the sound mode is either analog, VIDC10 compatible, or digital serial sound. I digital mode, serial sound data is output from this pin. In analog mode, the signal goes high between samples to allow for DAC settling.  SINK 141 I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the offield is selected. The horizontal timer system is unaffected by this signal.  SIREF 25 IA Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK 33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pin there is an internal pullup resistor to VDD, which should be left unconnected in normal mode.                                                                                                                                   | Name       | Pin                        | Type | Description                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| doubly-terminated 75 lines directly into a CRT.  RS 28 OA Right Analog Sound. Analog right hand stereo channel sound output.  SCLK 144 I Sound Clock. This signal can be used to clock the sound system, when a cloca synchronous to the video system is required. See Chapter 13.0 Sound.  SDCLK 3 OS8 Serial Data Clock. When the sound system is in serial sound mode, this clock output and validates serial data on its rising edge.  SDO/MUTE 4 OS8 Serial Data Out / Mute. This pin has two functions depending on whether it sound mode is either analog, VIDC10 compatible, or digital serial sound. In an analog mode, the signal goes high between samples to allow for DAC settling.  SINK 141 I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the offield is selected. The horizontal timer system is unaffected by this signal.  SIREF 25 IA Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK 33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pin there is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out. See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 87,88,102, | RCLK       | 124                        | I    | Reference Clock. See <i>Chapter 5.0 Pixel Clock</i> for details of the clocks into VIDC20. This clock may also drive the sound system.                                                                                                                                                            |  |

| SCLK 144 I Sound Clock. This signal can be used to clock the sound system, when a cloc asynchronous to the video system is required. See Chapter 13.0 Sound.  SDCLK 3 OS8 Serial Data Clock. When the sound system is in serial sound mode, this clock output and validates serial data on its rising edge.  SDO/MUTE 4 OS8 Serial Data Out / Mute. This pin has two functions depending on whether the sound mode is either analog, VIDC10 compatible, or digital serial sound. I digital mode, serial sound data is output from this pin. In analog mode, the signal goes high between samples to allow for DAC settling.  SINK 141 I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the of field is selected. The horizontal timer system is unaffected by this signal.  SIREF 25 IA Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK 33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pin normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan testing.  TMS 34 IP Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.                                                                                                               | ROUT       | 41                         | OA   | Red Analog Output. The video signal analog outputs are designed to drive doubly-terminated 75 lines directly into a CRT.                                                                                                                                                                          |  |

| asynchronous to the video system is required. See Chapter 13.0 Sound.  SDCLK  3 OS8 Serial Data Clock. When the sound system is in serial sound mode, this clock output and validates serial data on its rising edge.  SDO/MUTE  4 OS8 Serial Data Out / Mute. This pin has two functions depending on whether the sound mode is either analog, VIDC10 compatible, or digital serial sound. I digital mode, serial sound data is output from this pin. In analog mode, the signal goes high between samples to allow for DAC settling.  SINK  141 I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the of field is selected. The horizontal timer system is unaffected by this signal.  SIREF  25 IA Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK  33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pin there is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 4,445,59,78, 87,98,102,                                                                                                                                                                                                                  | RS         | 28                         | OA   | Right Analog Sound. Analog right hand stereo channel sound output.                                                                                                                                                                                                                                |  |

| output and validates serial data on its rising edge.  SDO/MUTE 4 OS8 Serial Data Out / Mute. This pin has two functions depending on whether it sound mode is either analog, VIDC10 compatible, or digital serial sound. I digital mode, serial sound data is output from this pin. In analog mode, the signal goes high between samples to allow for DAC settling.  SINK 141 I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the of field is selected. The horizontal timer system is unaffected by this signal.  SIREF 25 IA Sound Reference Current. A reference current must be fed into this pin in ordeto calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK 33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resiste to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pin There is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 4,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                 | SCLK       | 144                        | I    | Sound Clock. This signal can be used to clock the sound system, when a clock asynchronous to the video system is required. See <i>Chapter 13.0 Sound</i> .                                                                                                                                        |  |

| sound mode is either analog, VIDC10 compatible, or digital serial sound. I digital mode, serial sound data is output from this pin. In analog mode, the signal goes high between samples to allow for DAC settling.  SINK  141  I External Sink. This signal is used to synchronise VIDC20 with another vide system. When high, is set to zero, and in an interlaced display system, the od field is selected. The horizontal timer system is unaffected by this signal.  SIREF  25  IA Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK  33  IP Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI  35  IP Test Data In. Data for boundary scan testing is input to the chip on this pin there is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO  36  OS8  Test Data Out. Output data from boundary scan testing.  TMS  34  IP Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI  126  I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO  127  OS8  Phase Comparator Clock Out. See Chapter 5.0 Pixel Clock.  VCLKO  8,10,21,23, 44,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                                                                       | SDCLK      | 3                          | OS8  | Serial Data Clock. When the sound system is in serial sound mode, this clock is output and validates serial data on its rising edge.                                                                                                                                                              |  |

| system. When high, is set to zero, and in an interlaced display system, the offield is selected. The horizontal timer system is unaffected by this signal.  SIREF  25  IA  Sound Reference Current. A reference current must be fed into this pin in ord to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK  33  IP  Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI  35  IP  Test Data In. Data for boundary scan testing is input to the chip on this pin there is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO  36  OS8  Test Data Out. Output data from boundary scan testing.  TMS  34  IP  Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI  126  I  Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VDD  8,10,21,23, 44,45,59,78, 87,98,102,  Positive (+5V) Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SDO/MUTE   | 4                          | OS8  | Serial Data Out / Mute. This pin has two functions depending on whether the sound mode is either analog, VIDC10 compatible, or digital serial sound. In digital mode, serial sound data is output from this pin. In analog mode, this signal goes high between samples to allow for DAC settling. |  |

| to calibrate the sound DAC outputs. For most applications, a resistor to VDD sufficient, although a constant current source is recommended.  TCK  33 IP Test Clock. This is the boundary scan clock. There is an internal pullup resist to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this ping There is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan testing.  TMS 34 IP Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 44,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SINK       | 141                        | I    | External Sink. This signal is used to synchronise VIDC20 with another video system. When high, is set to zero, and in an interlaced display system, the odd field is selected. The horizontal timer system is unaffected by this signal.                                                          |  |

| to VDD, so this should normally be left unconnected.  TDI 35 IP Test Data In. Data for boundary scan testing is input to the chip on this pinchere is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan testing.  TMS 34 IP Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 44,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SIREF      | 25                         | IA   | Sound Reference Current. A reference current must be fed into this pin in order to calibrate the sound DAC outputs. For most applications, a resistor to <b>VDD</b> is sufficient, although a constant current source is recommended.                                                             |  |

| There is an internal pullup resistor to VDD, which should be left unconnected in normal mode.  TDO 36 OS8 Test Data Out. Output data from boundary scan testing.  TMS 34 IP Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI 126 I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO 127 OS8 Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.  VDD 8,10,21,23, 44,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | тск        | 33                         | IP   | Test Clock. This is the boundary scan clock. There is an internal pullup resistor to <b>VDD</b> , so this should normally be left unconnected.                                                                                                                                                    |  |

| TMS  34  IP  Test mode select. An input to the boundary scan logic, which should be legan unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI  126  I  Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO  127  OS8  Phase Comparator Clock Out. See Chapter 5.0 Pixel Clock.  VDD  8,10,21,23, 44,45,59,78, 87,98,102,  Positive (+5V) Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TDI        | 35                         | IP   |                                                                                                                                                                                                                                                                                                   |  |

| unconnected in normal mode since it has an internal pullup resistor to VDD.  VCLKI  126  I Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.  VCLKO  127  OS8  Phase Comparator Clock Out. See Chapter 5.0 Pixel Clock.  VDD  8,10,21,23, 44,45,59,78, 87,98,102,  Positive (+5V) Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TDO        | 36                         | OS8  | Test Data Out. Output data from boundary scan testing.                                                                                                                                                                                                                                            |  |

| VCLKO         127         OS8         Phase Comparator Clock Out. See Chapter 5.0 Pixel Clock.           VDD         8,10,21,23, 44,45,59,78, 87,98,102,         Positive (+5V) Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TMS        | 34                         | IP   | Test mode select. An input to the boundary scan logic, which should be left unconnected in normal mode since it has an internal pullup resistor to <b>VDD</b> .                                                                                                                                   |  |

| VDD 8,10,21,23, P Positive (+5V) Supply. 44,45,59,78, 87,98,102,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VCLKI      | 126                        | I    | Phase Comparator Clock In. See Chapter 5.0 Pixel Clock.                                                                                                                                                                                                                                           |  |

| 44,45,59,78,<br>87,98,102,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VCLKO      | 127                        | OS8  | Phase Comparator Clock Out.See Chapter 5.0 Pixel Clock.                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDD        | 44,45,59,78,<br>87,98,102, | P    | Positive (+5V) Supply.                                                                                                                                                                                                                                                                            |  |

| VDD_Analog 38 P Positive (+5V) supply for analog video system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VDD_Analog | 38                         | P    | Positive (+5V) supply for analog video system.                                                                                                                                                                                                                                                    |  |

| VDD_Sound 26 P Positive (+5V) supply for analog sound system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VDD_Sound  | 26                         | Р    | Positive (+5V) supply for analog sound system.                                                                                                                                                                                                                                                    |  |

**Table 1: Signal Description**

| Name       | Pin                                                      | Type | Description                                                                                                                                                                                                                                                                                                                                                                      |  |

|------------|----------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VIREF      | 37                                                       | IA   | Video Reference Current. The video DACs need a reference current in order to calibrate them. A constant current source is recommended, although a resistor up to <b>VDD</b> is sufficient for many applications.                                                                                                                                                                 |  |

| VnC        | 134                                                      | OS8  | Video NOT Cursor. This signal is used by the external memory controller to differentiate between video and cursor DMA requests.                                                                                                                                                                                                                                                  |  |

| vss        | 11,15,24,30,<br>43,52,66,77,<br>79,95,99,<br>122,128,137 | P    | Supply Ground.                                                                                                                                                                                                                                                                                                                                                                   |  |

| VSS_Analog | 42                                                       | P    | Supply ground for analog video system.                                                                                                                                                                                                                                                                                                                                           |  |

| VSS_Sound  | 29                                                       | P    | Supply ground for analog sound system.                                                                                                                                                                                                                                                                                                                                           |  |

| VSYNC      | 32                                                       | OS16 | Vertical Synchronisation. Dependant on the state of bits 19 and 18 in the external register, either vertical or a composite (XNOR) sync may be output on this pin, in either polarity. The width of the <b>VSYNC</b> pulse may be defined in units of a raster.                                                                                                                  |  |

| WS/LnR     | 2                                                        | OS8  | Word Select / Left NOT Right. Again, this pin has two functions depending on whether the sound mode is either analog or digital. In digital mode, this signal denotes whether the output serial data is for the left hand stereo channel (ws=0) or the right hand channel. In analog mode this signal gives the same stereo direction information, but the polarity is reversed. |  |

**Table 1: Signal Description**

## 2.1 Key to Signal Types

| I          | Input (TTL threshold)           | IP          | Input (TTL threshold) with pull up resistor |

|------------|---------------------------------|-------------|---------------------------------------------|

| IA         | Input Analog                    | <b>O</b> 4  | Output (4mA Drive)                          |

| <b>O</b> 8 | Output (8mÅ Drive)              | O16         | Output (16mA Drive)                         |

| OS8        | Output (8mA slew-limited drive) | <b>OS16</b> | Output (16mA slew-limited drive)            |

| OA         | Output Analog                   | P           | Power supply                                |

### 3.0 System Configurations

VIDC20 has a 64 bit data bus and there are four basic modes of bus operation. These are described below, with ARM memory controller examples. VIDC20 can be used with any memory controller which supports quad-word DMA -e.g. ARM's MEMC10.

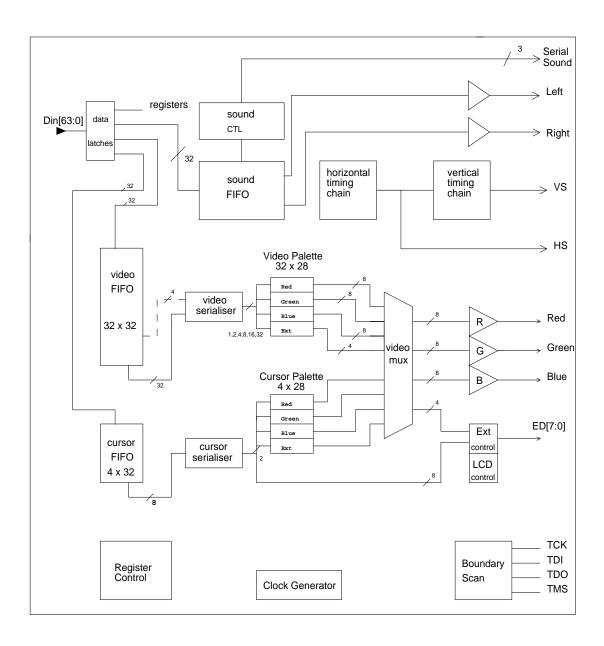

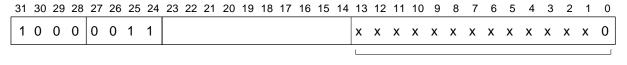

#### 3.1 Asynchronous 32-bit mode

This is the simplest mode, and in this configuration VIDC20 behaves almost exactly like VIDC10. Only the lower 32 bits of the data bus are used, and the upper 32 bits, though ignored, must be tied low.

VIDC20 makes requests for data to MEMC10 via the **nVIDRQ** line, and MEMC10 supplies the address to the single bank of DRAM of the next four words to be used. The four words of data come from the DRAM into the lower 32 data bits of VIDC20 and from there directly into the video FIFO within VIDC20.

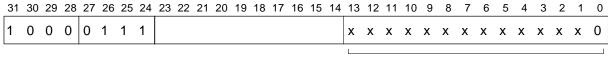

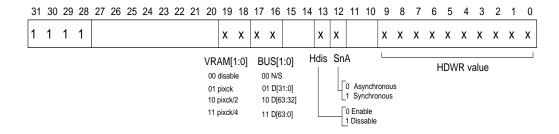

Similarly, VIDC20 requests data for the hardware cursor sprite when it is required (during the horizontal sync time), and this is supplied as four words out of a different area of the DRAM. This data passes into the same lower 32 data bits of VIDC20 and from there into the cursor FIFO within VIDC20. Finally, the registers within VIDC20 must be programmed. This is achieved by a processor write of the data into VIDC20 register addresses. Again the data is passed to VIDC20 on the lower 32 data bits. MEMC10 has an asynchronous DMA interface (i.e. the synchronisation is carried out within MEMC10). To configure VIDC20 for this mode, the **BUSCLK** input must be tied permanently LOW, the SnA bit in the Data Control Register set LOW, and BUS[1:0] in the Data Control Register programmed to value 01.

The frame buffer consists of a linear image in the DRAM. The start and end addresses of the buffer are programmable in MEMC10. The cursor buffer also consists of a (much smaller) linear image in the DRAM. The start address of this buffer is also programmable in MEMC10.

Figure 3: VIDC20 connected in Asynchronous 32 bit mode

#### 3.2 Synchronous 32-bit mode

This mode can be identical to the above mode, with the memory controller and VIDC20 both programmed to have an asynchronous interface like MEMC10 (SnA = 0), or the memory controller and VIDC20 can be configured to have a synchronous interface (SnA = 1). The latter is recommended, as it is more efficient and permits interlace to function correctly. Except for programming of the SnA bit, this mode is identical to the MEMC10 mode described above and so BUS[1:0] is programmed to value 01 again. This mode must be configured if dual-panel LCDs are to be used.

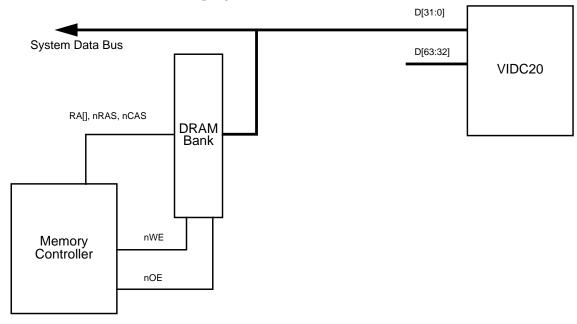

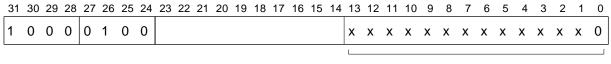

#### 3.3 64-bit mode

This is the standard configuration, and is an extension of the above mode. Again VIDC20 makes requests for data to the memory controller via the **nVIDRQ** line, but now the memory controller supplies the address to two banks of DRAM of the next eight words to be used. The four double-words of data come from both DRAM banks into the 64 data bits of VIDC20 and from there into the video FIFO within VIDC20 as 8 words. The two banks of DRAM are separated by a set of bidirectional buffers, and a simple PAL is required to control the DRAM enable lines and the buffers.

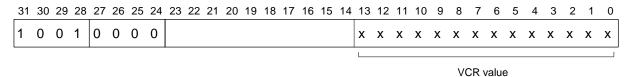

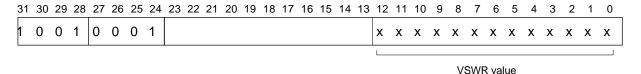

In this mode both the memory controller and VIDC20 must be programmed to have a synchronous interface (SnA = 1). VIDC20 is configured by setting BUS[1:0] to value 11 in the Data Control Register.

Figure 4: VIDC20 connected in 64 bit mode

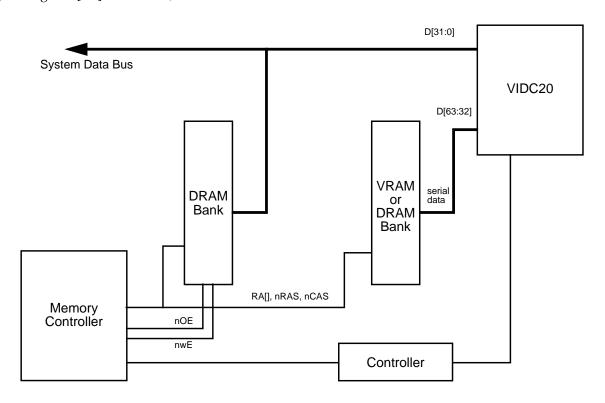

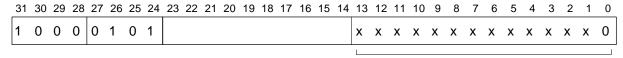

#### 3.4 Split Bank mode

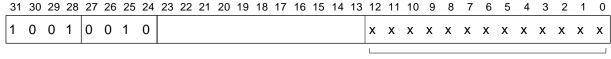

This configuration, is similar to the above, except that in this mode VIDC20 always receives video data on the upper 32 data bits only, and it receives cursor and programming data on the lower 32 bits only. Hence in this configuration the cursor and programming data come from one bank of DRAM, and the video data comes from a separate bank of RAM, which may be DRAM or VRAM. This mode is primarily intended for use with VRAM, and more details are given in the next section. If DRAM is used, then a buffer would be needed to separate the buses, and a simple PAL to control them. For split bank mode, VIDC20 is configured by setting BUS[1:0] to value 10, and SnA = 1.

Figure 5: VIDC20 connected in Split Bank mode

### 3.5 Using VRAM with VIDC20